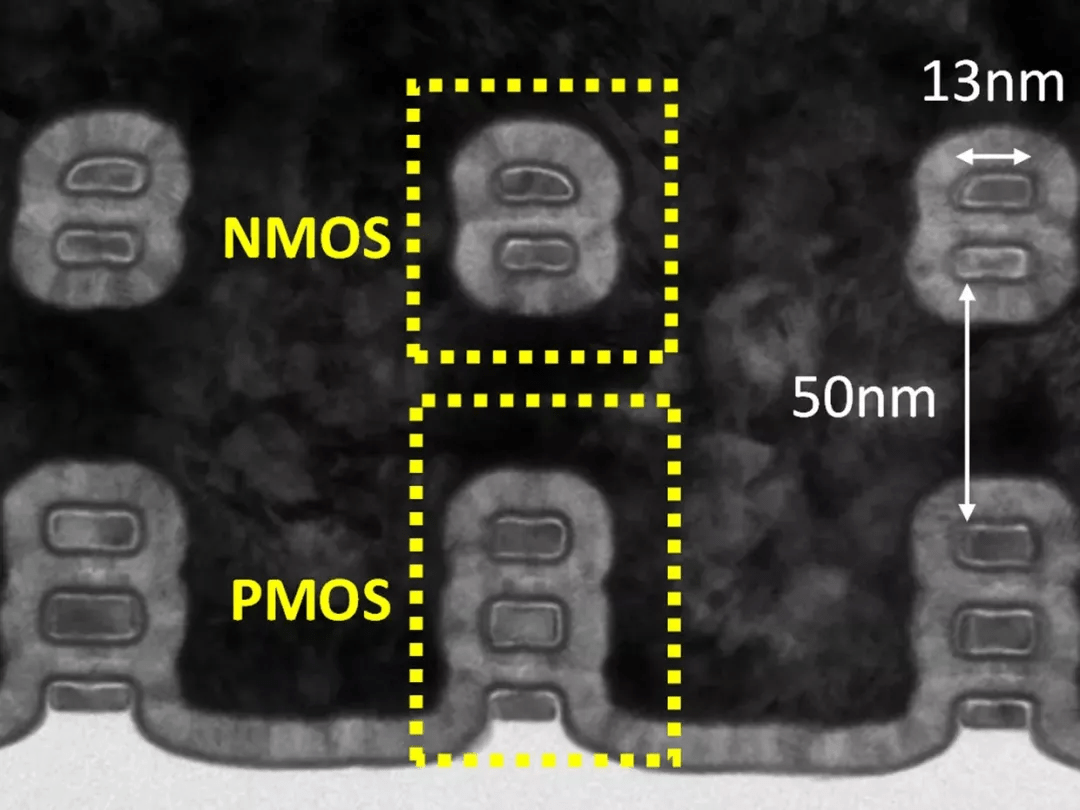

CMOS 芯片由成对的 N-MOS 和 P-MOS 器件组成 。 为了将更多器件塞入硅片中 , 芯片制造商希望将这两种类型的器件堆叠在一起 , 而不是并排排列 。 在去年 IEDM 上 , 英特尔展示了这样一种硅器件 , 称为互补 FET (CFET)。

文章图片

NMOS 和 PMOS 器件通常并排放置在芯片上 。 英特尔找到了一种将它们叠加在一起的方法 , 从而压缩了电路尺寸 。 图源:英特尔

吴燕庆教授领导的研究小组也尝试了同样的方法 , 他们用二硒化钨替换堆叠器件中的二硫化钼层 。 然后 , 通过修改源极和漏极之间的连接 , 2D CFET 变成了一个反相器电路 , 与单个晶体管的占位面积基本相同 。

在 2D 半导体获得大规模制造之前 , 显然还有很多工作要做 , 但随着接触电阻的进展和新实验的成功 , 我们可以期待这一领域的发展 。

原文链接:https://spectrum.ieee.org/2d-semiconductors-and-moores-law

推荐阅读

- 苏宁|可循环包装规模化应用 苏宁易购绿色物流再上新台阶

- IT|95306铁路货运电子商务平台升级上线 可24小时办理货运业务

- 硬件|Yukai推Amagami Ham Ham机器人:可模拟宠物咬指尖

- Apple|苹果高管解读AirPods 3代技术细节 暗示蓝牙带宽可能成为瓶颈

- 识别|天津滨海机场RFID行李全流程跟踪系统完成建设 行李标签识别成功率可提升至99%

- IT|新航空图像拍摄系统Microballoon:可重复使用且成本更低

- Microsoft|微软推Viva Insights插件 定时邮件可根据时区推荐发送时间

- Apple|法官称苹果零售店搜包和解协议虽不完美,但可继续进行

- 视点·观察|科技行业都在谈论“元宇宙”,可是它还不存在

- IT|为什么感染飙升但死亡人数有限?研究显示T细胞可防止奥密克戎引发重症