展开来看 , 应对不同的挑战 , 不同测试环节的测试参数和应用场景稍有区别 , 就需要采取不同的解决方案 。

对于复杂的供电问题 , 利用模块化的供电策略可以降低多相位复杂供电的困扰 。 通过灵活地分配测试资源 , 将电源拆解成一个个小的电源模块 , 任意组合成小的单元模块给不同的电源轨供电 , 同时还可以利用冗余的电源模块来帮助已经预设好的模块降低供电电源轨的稳压压力 。

简单举例 , 一个需要30安培的VDD引脚 , 如果每个通道支持5安培的输出能力 , 可以组合6个这样的单元来供电 , 同时利用冗余的通道组合单元与前面的6个单元组合在一起降低供电压力 。

此外 , 还可以利用软件编程的方式设定上电次序、软启动等 , 以减少外围供电电路 。

对于大多数应用处理器来说 , 工作频率与VDD一般呈现正相关性 。 在前期的设计验证中 , 厂商会尝试寻找sweet point使得芯片在有限的功耗下表现出更好的性能 , 在实际的生产测试中 , 可能会直接地设定一个指定的VDD , 看其能否在这个特定的VDD下达到预期的频率 。

文章图片

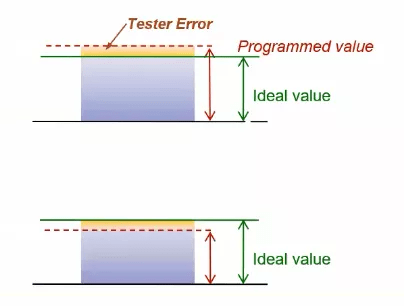

然而 , 在实际的测试中 , 没有一款测试机是完美的 。 实际操作中 , 芯片会经常性产生误差 , 一种方式是尝试编程稍高于芯片预设值的电压 , 由于考虑芯片的误差及所有的损耗 , 需要保证芯片引脚上的电压依然高于预期值 。 通过这种测试方法 , 即使仪表波动到最低的电压情况下 , 质量好的器件仍然可以pass , 从而获得更高的良率 。

另一种方式 , 直接将测试仪表的输出编程等于预期值 , 由于实际上一些测试机并不能达到良好的精准度 , 在一些情况下略低于输出 , 导致这部分的芯片实际测试电压低于预期值 。

这两种方式会造成不同的负面效果 。 在第一种的情况下 , VDD的预期值需要制定得更高一些 , 这样的话实际的电压会高于预期值 , 实际测试中的热损耗也会更大 , 在测试中就需要低速的向量帮助降温 。

第二种情况下 , 虽然实际出货的产品都能够pass预期值 , 但是对于一些误差比较大的机器 , 会造成额外的良率损失 。 对于7nm、5nm的先进制程产品来说 , 良率是极其重要的一个因素 , 由于先进制程产品尤其是晶圆面积较大时的良率本身非常低 , 在此基础上如果又额外损失一部分良率 , 这对于器件制造成本是难以接受的 。

面对种种挑战 , 我们该如何测试?测试机应该具备怎样的特性满足以上的诸多挑战需求呢?

四 , 不同测试挑战的对症下药

“Millivolts Matter” , 每一个毫伏的精度都非常重要 。 越来越低的核心电压对电源的输出精度 , 以及动态响应提出了越来越高的要求 。 泰瑞达一直把电源仪表的输出电压能力作为仪表设计最重要的参数之一 , 这也是泰瑞达区分于众多ATE厂商的特征之一 。

推荐阅读

- 星链|石豪:在太空,马斯克和美国当局是如何作恶的

- 快报|“他,是能成就导师的学生”

- 区块|面向2030:影响数据存储产业的十大应用(下):新兴应用

- 年轻人|人生缺少的不是运气,而是少了这些高质量订阅号

- 生活|气笑了,这APP的年度报告是在嘲讽我吧

- 于本|豆瓣 App 安卓新版本 7.20.0 测试

- bug|这款小工具让你的Win10用上“Win11亚克力半透明菜单”

- 苏宁|小门店里的暖心事,三位创业者的雪域坚守

- 历史|科普:詹姆斯·韦布空间望远镜——探索宇宙历史的“深空巨镜”

- 空间|(科技)科普:詹姆斯·韦布空间望远镜——探索宇宙历史的“深空巨镜”